| Version 15 (modified by , 6 years ago) ( diff ) |

|---|

Serial Peripheral Interface Bus (SPI)

The Serial Peripheral Interface bus is a synchronous serial communication interface specification used for short distance communication primary in embedded systems. The interface was originally developed by Motorola and can be used in a master or slave configuration. It is typically used as a 3-wire bus containing the following signals (other than power and ground and chip-selects):

- SCLK

- MISO

- MOSI

- SS# (Optional Slave Select)

SPI can be a multi-slave bus if chip selects are used which are asserted by the host controller to enable one device at a time.

References:

On-Board SPI controllers

The following Gateworks boards support on-board SPI controllers:

| Family | Board | Connector | Notes |

|---|---|---|---|

| Newport | GW640x | J8 | single CS2; spi_7_0 dts node; half-duplex1; modes 13 |

| GW630x | J8 | single CS2; spi_7_0 dts node; half-duplex1; modes 13 | |

| GW620x | J5 | single CS2; spi_7_0 dts node; half-duplex1; modes 13 | |

| GW610x | J10 | single CS2; spi_7_0 dts node; half-duplex1; modes 13 | |

| Ventana | GW54xx-E+ | J24 | single CS2; ecspi2 dts node |

| GW522x | J32 | single CS2; ecspi3 dts node | |

| GW5910 | J11 | single CS2; ecspi3 dts node | |

| Laguna | GW2388 | J9 |

- Note that the Cavium ThunderX SPI controller in the CN80XX on the Newport Product family only supports half-duplex SPI transfers. In hardware the connections are full duplex MISO and MOSI lines are not shared, in software reads and writes need to be sent in separate calls, rather than simultaneously (full duplex). Drivers that use full-duplex transactions can be modified to support half-duplex (see can:mcp251x: convert driver to half-duplex SPI as en example.

- While only a single Chip Select (CS) is brought out to an external connector and of the DIO pins routed to ARM GPIO's can be used as additional chip-selects. For Ventana this is done via device-tree pinctrl and for Newport this must be done via a PINSEL GPIO (contact support@…)

- Note that the Cavium ThunderX SPI controller in the CN80XX only supports SPI mode 1 (which clock polarity (CPOL/CKP) is low, clock phase (CPHA) is high, and Clock edge (CKE/NCPHA) is low.

See the below product family specific sections for pinout details.

Newport

Gateworks Newport boards support 3.3V TTL SPI up to 50MHz clock to an off-board expansion connector with the following pinout:

- 1 - MOSI

- 2 - MISO

- 3 - SCLK (Up to 50MHz clock supported)

- 4 - SS0# (This is chip select 0)

- 5 - 3.3V

- GND

Notes:

- While only a single Chip Select (CS) is brought out to an external connector and of the DIO pins routed to ARM GPIO's can be used as additional chip-selects (contact support@… for details)

- Note that the Cavium ThunderX SPI controller in the CN80XX on the Newport Product family only supports half-duplex SPI transfers. Drivers that use full-duplex transactions can be modified to support half-duplex (see can:mcp251x: convert driver to half-duplex SPI as en example.

- Note that the Cavium ThunderX SPI controller in the CN80XX only supports SPI mode 1 (which clock polarity (CPOL/CKP) is low, clock phase (CPHA) is high, and Clock edge (CKE/NCPHA) is low.

You need to add a device-tree node to the SPI controller to use a kernel driver. Note that you can also access SPI from userspace using spidev (see below)

An example device-tree child node for a Spansion m25p128 compatible device (S25FL128) 128Mbit (16MB) SPI NOR FLASH device would be:

&spi_7_0 { flash: m25p80@0 { compatible = "spansion,m25p128", "jedec,spi-nor"; spi-max-frequency = <30000000>; reg = <0>; #address-cells = <1>; #size-cells = <1>; m25p,fast-read; partition@0 { label = "data"; reg = <0x0 0x1000000>; }; }; };

- Note that this node must appear within the SPI host controller node (&spi_7_0) along with any other devices on the SPI bus.

- Note that the values shown in the above node are specific to the m25p128, and can vary greatly from the actual device you are using. Replace attribute values as necessary.

- When searching for your device ID string or its controlling driver, searching via a Linux LXR site like the one at missing link electronics for your device name can be helpful.

Ventana

Gateworks Ventana boards support 3.3V TTL SPI to an off-board expansion connector with the following pinout:

- 1 - MOSI

- 2 - MISO

- 3 - SCLK

- 4 - SS0# (This is chip select 0)

- 5 - 3.3V

- GND

Notes:

- While only a single Chip Select (CS) is brought out to an external connector and of the DIO pins routed to ARM GPIO's can be used as additional chip-selects. For Ventana this is done via device-tree pinctrl.

You need to add add a device-tree node to the SPI controller to use a kernel driver. Note that you can also access SPI from userspace using spidev (see below)

An example device-tree child node for a Spansion m25p128 compatible device (S25FL128) 128Mbit (16MB) SPI NOR FLASH device would be:

&ecspi2 { flash: m25p80@0 { compatible = "spansion,m25p128", "jedec,spi-nor"; spi-max-frequency = <30000000>; reg = <0>; #address-cells = <1>; #size-cells = <1>; m25p,fast-read; partition@0 { label = "data"; reg = <0x0 0x1000000>; }; }; };

- Note that this node must appear within the SPI host controller. For a list of device-tree nodes see above.

- Note that the values shown in the above node are specific to the m25p128, and can vary greatly from the actual device you are using. Replace attribute values as necessary.

- When searching for your device ID string or its controlling driver, searching via a Linux LXR site like the one at missing link electronics for your device name can be helpful.

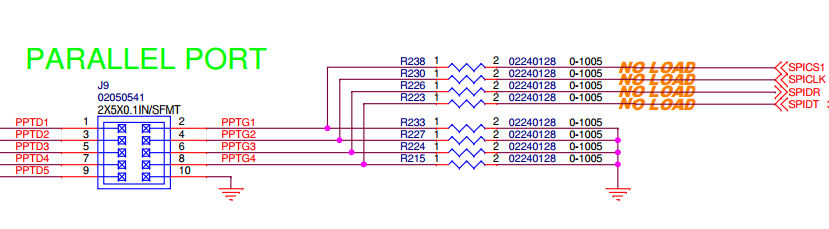

Laguna

Gateworks Laguna boards support 3.3V TTL SPI to an off-board expansion connector with the following pinout:

- J9.2 - CS#

- J9.4 - SCLK

- J9.6 - MISO

- J9.8 - MOSI

- J9.10 - GND

Notes:

- The SPI bus is shared with the alternate flash device

- For details on adding kernel devices to the Laguna kernel see below

The Laguna Linux kernels which does not use device-tree needs to register a spi_board_info struct with the kernel via spi_register_board_info(). To add a SPI device to Laguna you would add it to the spi_board_info array in laguna.c. Be sure to specify chip_select=1 to use CS1 as CS0 is used for the on-board SPI FLASH device:

USB SPI controllers

A SPI master can also be added via USB expansion. For example:

- GW16113 firmware-flexible USB 2.0 FS expansion

- Commell MPX-24794S USB 2.0 FS SPI/I2C/GPIO expansion

Linux spidev userspace API

SPI devices have a limited userspace API, supporting basic half-duplex read() and write() access to SPI slave devices referred to as spidev. Using ioctl() requests, full duplex transfers and device I/O configuration are also available.

Some reasons you might want to use this programming interface include:

- Prototyping in an environment that's not crash-prone; stray pointers in userspace won't normally bring down any Linux system.

- Developing simple protocols used to talk to micro-controllers acting as SPI slaves, which you may need to change quite often.

Of course there are drivers that can never be written in userspace, because they need to access kernel interfaces (such as IRQ handlers or other layers of the driver stack) that are not accessible to userspace.

Userspace access to SPI devices is done through the /dev/spidev<bus>.<chip-select> device interface. In order to use this you must have spidev enabled in the kernel (CONFIG_SPI_SPIDEV) and have a spidev node defined under the SPI controller in the device-tree.

In order to support spidev a spidev child node needs to be present in the device-tree under the SPI host controller. For example, a GW54xx which brings out the ecspi2 host interface:

&ecspi2 { cs-gpios = <&gpio2 26 GPIO_ACTIVE_HIGH>; pinctrl-names = "default"; pinctrl-0 = <&pinctrl_ecspi2>; status = "okay"; spidev0: spidev@0 { compatible = "rohm,dh2228fv"; reg = <0>; spi-max-frequency = <60000000>; }; };

For instructions on compiling and updating a device-tree see linux/devicetree

An application using spidev would include the <linux/spi/spidev.h> header file.

For more info see:

Attachments (2)

- GW5220-SPI-INTERFACE.png (13.4 KB ) - added by 8 years ago.

- spi2388.png (32.8 KB ) - added by 8 years ago.

Download all attachments as: .zip