| Version 22 (modified by , 21 months ago) ( diff ) |

|---|

Gateworks FCC/CE Certification

FCC & CE testing must be done on the complete system which includes enclosure, cables, radios, antenna, power supply, etc. Because of this, we do not provide FCC/CE certifications on individual boards. Gateworks can however work with your certification house on getting your complete system through certification.

All of our products have been designed to reduce both conducted and radiated emissions and most customers make it through the approval process with minimal effort, assuming they have an adequate enclosure solution. We can also work directly with your certification house to provide the necessary documents for the certification process.

Below are some baseline scans for the standard Ventana SBC models in our metal indoor enclosures with a PoE powersupply. Note these are baseline scans and FCC certification must be performed on your specific system which includes any peripheral cards, cables, antenna, power supplies, etc so results will vary depending on your configuration.

FCC Testing Categories

Unintentional Radiators - Devices which don't transmit RF. As an example, a Gateworks SBC without Radio. Certification cost is considerably less than a system with an intentional radiator.

Intentional Radiators - Devices which transmit RF as part of their standard operation. As an example, a Gateworks SBC with Radio installed in one of the Mini-PCIe sites (Wifi, Cellular, Bluetooth, etc.). Certification is more extensive and costly to make sure the transmitted RF is within allotted specifications. If a pre-certified radios is used (in same manner/setup as manufacturers certification) transmitter testing can sometimes be eliminated allowing testing as an unintentional radiator at reduced cost. Check with your certification house for details and requirements.

FCC Tips

Tips for passing emissions include, but not limited to:

- Use a metal enclosure with minimal openings. Make sure if the enclosure is painted that the paint is removed/masked in areas that come in direct contact with the connector shields. For example, the Ethernet RJ45 shields should make direct contact with the enclosure metal. Any paint in the cutout hole should be removed/masked.

- Use shielded cables for power, Ethernet, USB, etc. Make sure the shields are terminated at both ends during testing. See below for shielded vs non-shielded RJ45 connectors.

Non-shielded RJ45

Shielded RJ45

- Proper grounding of the board, enclosure, cables and power supply. Gateworks boards typically have several mounting holes with options to tie these mounting holes to either digital or chassis ground. There are also options for tying chassis and digital ground together. Contact support for the various options for each board.

- Use pre-certified wifi radios. By using a pre-certified radio you can avoid having to re-certify the radio which can be more expensive since it is classified as a transmitting device. Note you must use the radio in the same configuration and with same antenna (gain) as it was certified. Check with your certification house for exact rules and regulations.

- A handy method to view the emitting clocks on a Venice board is to use the command:

cat /sys/kernel/debug/clk/clk_summary

root@mesh-10-2:~# cat /sys/kernel/debug/clk/clk_summary

enable prepare protect duty hardware

clock count count count rate accuracy phase cycle enable

-------------------------------------------------------------------------------------------------------

sys_pll2 1 1 0 1000000000 0 0 50000 Y

sys_pll2_out 7 7 0 1000000000 0 0 50000 Y

sys_pll2_1000m 0 0 0 1000000000 0 0 50000 Y

disp_axi 0 0 0 500000000 0 0 50000 N

disp_axi_root_clk 0 0 0 500000000 0 0 50000 N

sys_pll2_500m 1 1 0 500000000 0 0 50000 Y

nand 0 0 0 500000000 0 0 50000 N

nand_root_clk 0 0 0 500000000 0 0 50000 N

usb_bus 2 2 0 500000000 0 0 50000 Y

usb1_ctrl_root_clk 1 1 0 500000000 0 0 50000 Y

sys_pll2_333m 1 1 0 333333333 0 0 50000 Y

main_axi 1 1 0 333333333 0 0 50000 Y

sys_pll2_250m 1 1 0 250000000 0 0 50000 Y

pcie1_ctrl 1 1 0 250000000 0 0 50000 Y

pcie1_root_clk 1 1 0 250000000 0 0 50000 Y

sys_pll2_200m 1 1 0 200000000 0 0 50000 Y

ecspi3 0 0 0 50000000 0 0 50000 N

ecspi3_root_clk 0 0 0 50000000 0 0 50000 N

ecspi2 1 1 0 50000000 0 0 50000 Y

ecspi2_root_clk 2 2 0 50000000 0 0 50000 Y

ecspi1 0 0 0 50000000 0 0 50000 N

ecspi1_root_clk 0 0 0 50000000 0 0 50000 N

arm_m4_core 0 0 0 200000000 0 0 50000 N

sys_pll2_166m 0 0 0 166666666 0 0 50000 Y

sys_pll2_125m 1 1 0 125000000 0 0 50000 Y

enet_ref 1 1 0 125000000 0 0 50000 Y

sys_pll2_100m 2 2 0 100000000 0 0 50000 Y

pcie1_phy 0 0 0 100000000 0 0 50000 N

gic 1 1 0 100000000 0 0 50000 Y

enet_timer 1 1 0 100000000 0 0 50000 Y

sys_pll2_50m 2 2 0 50000000 0 0 50000 Y

pcie1_aux 1 1 0 10000000 0 0 50000 Y

enet_phy 1 1 0 50000000 0 0 50000 Y

sys_pll1 1 1 0 800000000 0 0 50000 Y

sys_pll1_out 4 4 0 800000000 0 0 50000 Y

sys_pll1_800m 2 2 0 800000000 0 0 50000 Y

disp_apb 0 0 0 200000000 0 0 50000 N

disp_apb_root_clk 0 0 0 200000000 0 0 50000 N

vpu_bus 0 0 0 800000000 0 0 50000 N

vpu_dec_root_clk 0 0 0 800000000 0 0 50000 N

gpu_ahb 0 0 0 400000000 0 0 50000 N

gpu_axi 0 0 0 800000000 0 0 50000 N

gpu_root_clk 0 0 0 800000000 0 0 50000 N

audio_ahb 1 1 0 400000000 0 0 50000 Y

ipg_audio_root 1 2 0 400000000 0 0 50000 Y

sdma3_clk 0 2 0 400000000 0 0 50000 N

sdma2_clk 4 2 0 400000000 0 0 50000 Y

pdm_ipg_clk 0 0 0 400000000 0 0 50000 N

sai6_ipg_clk 0 0 0 400000000 0 0 50000 N

sai5_ipg_clk 0 0 0 400000000 0 0 50000 N

sai4_ipg_clk 0 0 0 400000000 0 0 50000 N

sai3_ipg_clk 0 0 0 400000000 0 0 50000 N

sai2_ipg_clk 0 0 0 400000000 0 0 50000 N

sai1_ipg_clk 0 0 0 400000000 0 0 50000 N

arm_a53_div 0 0 0 800000000 0 0 50000 N

dram_apb 1 1 0 160000000 0 0 50000 Y

sys_pll1_400m 0 0 0 400000000 0 0 50000 Y

usdhc3 0 0 0 400000000 0 0 50000 N

usdhc3_root_clk 0 0 0 400000000 0 0 50000 N

usdhc2 0 0 0 200000000 0 0 50000 N

usdhc2_root_clk 0 0 0 200000000 0 0 50000 N

usdhc1 0 0 0 200000000 0 0 50000 N

usdhc1_root_clk 0 0 0 200000000 0 0 50000 N

qspi 0 0 0 400000000 0 0 50000 N

qspi_root_clk 0 0 0 400000000 0 0 50000 N

sys_pll1_266m 2 2 0 266666666 0 0 50000 Y

nand_usdhc_bus 1 1 0 266666666 0 0 50000 Y

nand_usdhc_rawnand_clk 0 0 0 266666666 0 0 50000 N

enet_axi 1 1 0 266666666 0 0 50000 Y

enet1_root_clk 2 2 0 266666666 0 0 50000 Y

sys_pll1_200m 0 0 0 200000000 0 0 50000 Y

sys_pll1_160m 0 0 0 160000000 0 0 50000 Y

sys_pll1_133m 1 1 0 133333333 0 0 50000 Y

ahb 5 4 0 133333333 0 0 50000 Y

ipg_root 7 7 0 66666667 0 0 50000 Y

sdma1_clk 2 1 0 66666667 0 0 50000 Y

tmu_root_clk 1 1 0 66666667 0 0 50000 Y

ocotp_root_clk 0 0 0 66666667 0 0 50000 N

mu_root_clk 0 0 0 66666667 0 0 50000 N

gpio5_root_clk 1 1 0 66666667 0 0 50000 Y

gpio4_root_clk 1 1 0 66666667 0 0 50000 Y

gpio3_root_clk 0 0 0 66666667 0 0 50000 N

gpio2_root_clk 1 1 0 66666667 0 0 50000 Y

gpio1_root_clk 1 1 0 66666667 0 0 50000 Y

sys_pll1_100m 1 1 0 100000000 0 0 50000 Y

usb_phy_ref 1 1 0 100000000 0 0 50000 Y

dram_alt 0 0 0 100000000 0 0 50000 N

dram_alt_root 0 0 0 25000000 0 0 50000 Y

sys_pll1_80m 0 0 0 80000000 0 0 50000 Y

sys_pll1_40m 0 0 0 40000000 0 0 50000 Y

wrclk 0 0 0 40000000 0 0 50000 N

dummy 0 0 0 0 0 0 50000 Y

pcie0-refclk 2 2 0 100000000 0 0 50000 Y

clk_ext4 0 0 0 133000000 0 0 50000 Y

clk_ext3 0 0 0 133000000 0 0 50000 Y

clk_ext2 0 0 0 133000000 0 0 50000 Y

clk_ext1 0 0 0 133000000 0 0 50000 Y

osc_24m 7 11 0 24000000 0 0 50000 Y

gpt_3m 0 0 0 3000000 0 0 50000 Y

vpu_h1 0 0 0 24000000 0 0 50000 N

vpu_h1_root_clk 0 0 0 24000000 0 0 50000 N

pdm 0 0 0 24000000 0 0 50000 N

pdm_root_clk 0 0 0 24000000 0 0 50000 N

pcie2_aux 0 0 0 24000000 0 0 50000 N

pcie2_phy 0 0 0 24000000 0 0 50000 N

pcie2_ctrl 0 0 0 24000000 0 0 50000 N

csi2_esc 0 0 0 24000000 0 0 50000 N

csi2_phy_ref 0 0 0 24000000 0 0 50000 N

csi2_core 0 0 0 24000000 0 0 50000 N

csi1_esc 0 0 0 24000000 0 0 50000 N

csi1_phy_ref 0 0 0 24000000 0 0 50000 N

csi1_core 0 0 0 24000000 0 0 50000 N

csi1_root_clk 0 0 0 24000000 0 0 50000 N

dsi_dbi 0 0 0 24000000 0 0 50000 N

dsi_phy_ref 0 0 0 24000000 0 0 50000 N

dsi_core 0 0 0 24000000 0 0 50000 N

clko2 0 0 0 24000000 0 0 50000 N

clko1 0 0 0 24000000 0 0 50000 N

wdog 1 1 0 24000000 0 0 50000 Y

wdog3_root_clk 0 0 0 24000000 0 0 50000 N

wdog2_root_clk 0 0 0 24000000 0 0 50000 N

wdog1_root_clk 1 1 0 24000000 0 0 50000 Y

gpt1 0 0 0 24000000 0 0 50000 N

gpt1_root_clk 0 0 0 24000000 0 0 50000 N

pwm4 0 0 0 24000000 0 0 50000 N

pwm4_root_clk 0 0 0 24000000 0 0 50000 N

pwm3 0 0 0 24000000 0 0 50000 N

pwm3_root_clk 0 0 0 24000000 0 0 50000 N

pwm2 0 0 0 24000000 0 0 50000 N

pwm2_root_clk 0 0 0 24000000 0 0 50000 N

pwm1 0 0 0 24000000 0 0 50000 N

pwm1_root_clk 0 0 0 24000000 0 0 50000 N

usb_core_ref 0 0 0 24000000 0 0 50000 N

uart4 0 0 0 24000000 0 0 50000 N

uart4_root_clk 0 0 0 24000000 0 0 50000 N

uart3 0 0 0 24000000 0 0 50000 N

uart3_root_clk 0 0 0 24000000 0 0 50000 N

uart2 1 1 0 24000000 0 0 50000 Y

uart2_root_clk 4 4 0 24000000 0 0 50000 Y

uart1 0 0 0 24000000 0 0 50000 N

uart1_root_clk 0 0 0 24000000 0 0 50000 N

i2c4 0 0 0 24000000 0 0 50000 N

i2c4_root_clk 0 0 0 24000000 0 0 50000 N

i2c3 0 1 0 24000000 0 0 50000 N

i2c3_root_clk 0 1 0 24000000 0 0 50000 N

i2c2 0 1 0 24000000 0 0 50000 N

i2c2_root_clk 0 1 0 24000000 0 0 50000 N

i2c1 0 1 0 24000000 0 0 50000 N

i2c1_root_clk 0 1 0 24000000 0 0 50000 N

spdif2 0 0 0 24000000 0 0 50000 N

spdif1 0 0 0 24000000 0 0 50000 N

sai6 0 0 0 24000000 0 0 50000 N

sai6_root_clk 0 0 0 24000000 0 0 50000 N

sai5 0 0 0 24000000 0 0 50000 N

sai5_root_clk 0 0 0 24000000 0 0 50000 N

sai4 0 0 0 24000000 0 0 50000 N

sai4_root_clk 0 0 0 24000000 0 0 50000 N

sai2 0 0 0 24000000 0 0 50000 N

sai2_root_clk 0 0 0 24000000 0 0 50000 N

sai1 0 0 0 24000000 0 0 50000 N

sai1_root_clk 0 0 0 24000000 0 0 50000 N

lcdif_pixel 0 0 0 24000000 0 0 50000 N

dc_pixel 0 0 0 24000000 0 0 50000 N

disp_dc8000 0 0 0 24000000 0 0 50000 N

disp_root_clk 0 0 0 24000000 0 0 50000 N

disp_dtrc 0 0 0 24000000 0 0 50000 N

noc_apb 1 1 0 24000000 0 0 50000 Y

disp_rtrm 0 0 0 24000000 0 0 50000 N

disp_rtrm_root_clk 0 0 0 24000000 0 0 50000 N

gpu2d_core 0 0 0 24000000 0 0 50000 N

gpu2d_root_clk 0 0 0 24000000 0 0 50000 N

gpu3d_core 0 0 0 24000000 0 0 50000 N

gpu3d_root_clk 0 0 0 24000000 0 0 50000 N

sys_pll3_ref_sel 1 1 0 24000000 0 0 50000 Y

sys_pll3 1 1 0 750000000 0 0 50000 Y

sys_pll3_bypass 1 1 0 750000000 0 0 50000 Y

sys_pll3_out 1 1 0 750000000 0 0 50000 Y

noc 1 1 0 750000000 0 0 50000 Y

arm_pll_ref_sel 1 1 0 24000000 0 0 50000 Y

arm_pll 1 1 0 1200000000 0 0 50000 Y

arm_pll_bypass 1 1 0 1200000000 0 0 50000 Y

arm_pll_out 1 1 0 1200000000 0 0 50000 Y

arm_a53_core 1 1 0 1200000000 0 0 50000 Y

arm 1 1 0 1200000000 0 0 50000 Y

vpu_core 0 0 0 1200000000 0 0 50000 N

vpu_pll_ref_sel 0 1 0 24000000 0 0 50000 Y

vpu_pll 0 1 0 600000000 0 0 50000 Y

vpu_pll_bypass 0 1 0 600000000 0 0 50000 Y

vpu_pll_out 0 2 0 600000000 0 0 50000 N

vpu_g2 0 1 0 600000000 0 0 50000 N

vpu_g2_root_clk 0 1 0 600000000 0 0 50000 N

vpu_g1 0 1 0 600000000 0 0 50000 N

vpu_g1_root_clk 0 1 0 600000000 0 0 50000 N

gpu_pll_ref_sel 0 0 0 24000000 0 0 50000 Y

gpu_pll 0 0 0 800000000 0 0 50000 Y

gpu_pll_bypass 0 0 0 800000000 0 0 50000 Y

gpu_pll_out 0 0 0 800000000 0 0 50000 N

dram_pll_ref_sel 1 1 0 24000000 0 0 50000 Y

dram_pll 1 1 0 750000000 0 0 50000 Y

dram_pll_bypass 1 1 0 750000000 0 0 50000 Y

dram_pll_out 1 1 0 750000000 0 0 50000 Y

dram_core_clk 1 1 0 750000000 0 0 50000 Y

video_pll1_ref_sel 0 0 0 24000000 0 0 50000 Y

video_pll1 0 0 0 594000000 0 0 50000 Y

video_pll1_bypass 0 0 0 594000000 0 0 50000 Y

video_pll1_out 0 0 0 594000000 0 0 50000 N

audio_pll2_ref_sel 0 0 0 24000000 0 0 50000 Y

audio_pll2 0 0 0 650000000 0 0 50000 Y

audio_pll2_bypass 0 0 0 650000000 0 0 50000 Y

audio_pll2_out 0 0 0 650000000 0 0 50000 N

audio_pll1_ref_sel 0 0 0 24000000 0 0 50000 Y

audio_pll1 0 0 0 393216000 0 0 50000 Y

audio_pll1_bypass 0 0 0 393216000 0 0 50000 Y

audio_pll1_out 0 0 0 393216000 0 0 50000 N

sai3 0 0 0 24576000 0 0 50000 N

sai3_root_clk 0 0 0 24576000 0 0 50000 N

clkout2_sel 0 0 0 393216000 0 0 50000 Y

clkout2_div 0 0 0 393216000 0 0 50000 Y

clkout2 0 0 0 393216000 0 0 50000 N

clkout1_sel 0 0 0 393216000 0 0 50000 Y

clkout1_div 0 0 0 393216000 0 0 50000 Y

clkout1 0 0 0 393216000 0 0 50000 N

osc_32k 0 0 0 32768 0 0 50000 Y

root@mesh-10-2:~#

Clocks on Venice SBCs

The Venice SBCs contain many interfaces and use the following base clocks for these interfaces. Note that depending on the particular Venice board model, not all of these interfaces may be present or loaded.

Below sample data is from a GW7200-00:

- i.MX8M Mini CPU

- 24MHz Main clock (typically Y1 crystal)

- 32.768KHz RTC clock

- Gateworks System Controller (GSC)

- 32.768KHz RTC clock (typically Y3 crystal)

- USB Hub

- 25.000MHz (typically Y1, crystal)

- Ethernet Phy (RGMII)

- 25.000MHz (typically Y2 crystal)

- PCIe Clock Generator

- 100.000MHz (IC clockgen chip)

- Gigabit Ethernet Controller

- 25.000MHz (can be Y2, crystal)

- DC/DC Converter(s)

- 609KHz

Please contact Gateworks support for further questions.

Ventana SBCs

The Ventana SBCs contain many interfaces and use the following base clocks for these interfaces. Note that depending on the particular Ventana board model, not all of these interfaces may be present or loaded.

- i.MX6 CPU

- 24MHz Main clock

- 32.768KHz RTC clock

- Gateworks System Controller (GSC)

- 32.768KHz RTC clock

- USB Hub

- 24.000MHz

- Ethernet Phy

- 25.000MHz

- Analog Video Input

- 28.63636MHz

- PCIe Clock Generator

- 25.000MHz

- Gigabit Ethernet Controller

- 25.000MHz

- HDMI Video Input

- 27.000MHz

- DC/DC Converter

- 280KHz

The following preliminary scans are for: FCC EN55022 Class: B

Conducted Emissions

Conducted emissions are those that are on a conductor, such as a power or ethernet cable . In the case of using an AC to DC converted connected to a wall, the converter will provide protection. The majority of our customers typically use an AC/DC supply to generate the DC voltage to our board so the conducted emissions are tested on the AC/DC supply and not directly on our DC input. If using an external power supply, explore the option to have the testing done on the AC input of that supply.

The DC/DC converter we use on some of the Ventana boards does have a switching frequency at 280KHz so this will show up on conducted emission testing. In most cases customers are using an AC/DC converter so the conducted emissions is measured on the AC input main instead of the DC. For cases where the DC needs to pass we suggest they use an input filter.

Common solutions include:

- Install a ferrite around the power cable

- Something with a low frequency would be best if trying to eliminate 280KHz and it's harmonics. Here is a link for a snap-on core to try. The snap-on is more expensive than a solid core so once proofed out it may be considered to change to a solid core. Note it is also possible to loop the power wire several times through the core and the more loops made the more attenuation.

- Typically a large in-line inductor (around 22uH on +VCC input) will provide enough filtering. Note that this inductor has to be sized to handle the amount of current the board is drawing under load. Locate it as close as possible to the board. Note that the inductor will slow the rise/fall time of the input voltage so test with a particular configuration to make sure there are no start-up issues. These inductors can be quite large, especially for high current applications.

- Here would be a suggested example part: http://www.digikey.com/product-detail/en/abracon-llc/AIAP-02-180K/AIAP-02-180K-ND/3059868

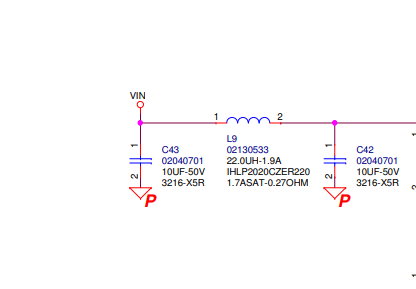

- Put a Pi filter inline with the power cable, such example is below (values may need to be adjusted)

- Note that the component values would need to be tested and make sure they don’t cause any adverse effects in your system. The use of an inductor in series slows the transient response of the input voltage so when radios transmit this could cause the DC/DC to “starve” for voltage. It is best to setup the Pi filter and then do some testing (actually put a scope probe to the input voltage at the board) and make sure there isn't any visible large dips during radio transmit.

- Input caps: 10uF/100V

- Series Inductor: 22uH, >6A rated

- Output caps: There typically is 10uF of capacitance on the board but an additional 10uF/100V would be good if possible.

- Here is the topology:

- Input -------caps to gnd ------- series inductor ------- caps to gnd----- output to board

- Example schematic:

Attachments (8)

- gw5100emienclosure.png (112.3 KB ) - added by 8 years ago.

- gw5200emibare.png (131.7 KB ) - added by 8 years ago.

- gw5200emienclosure.png (119.4 KB ) - added by 8 years ago.

- gw5300emienclosure.png (124.3 KB ) - added by 8 years ago.

- gw5400enclosure.png (117.7 KB ) - added by 8 years ago.

- pifilter.png (12.7 KB ) - added by 7 years ago.

- nonshield.PNG (140.3 KB ) - added by 5 years ago.

- shield.PNG (192.5 KB ) - added by 5 years ago.

Download all attachments as: .zip