Getting Started

Newport Software

Peripherals

User Manuals

Wireless / WiFi Radios

Cellular Modems

GPS

3D Model

Getting Started |

Newport Software |

Peripherals |

User Manuals |

|

Wireless / WiFi Radios |

Cellular Modems |

GPS |

3D Model |

}}}

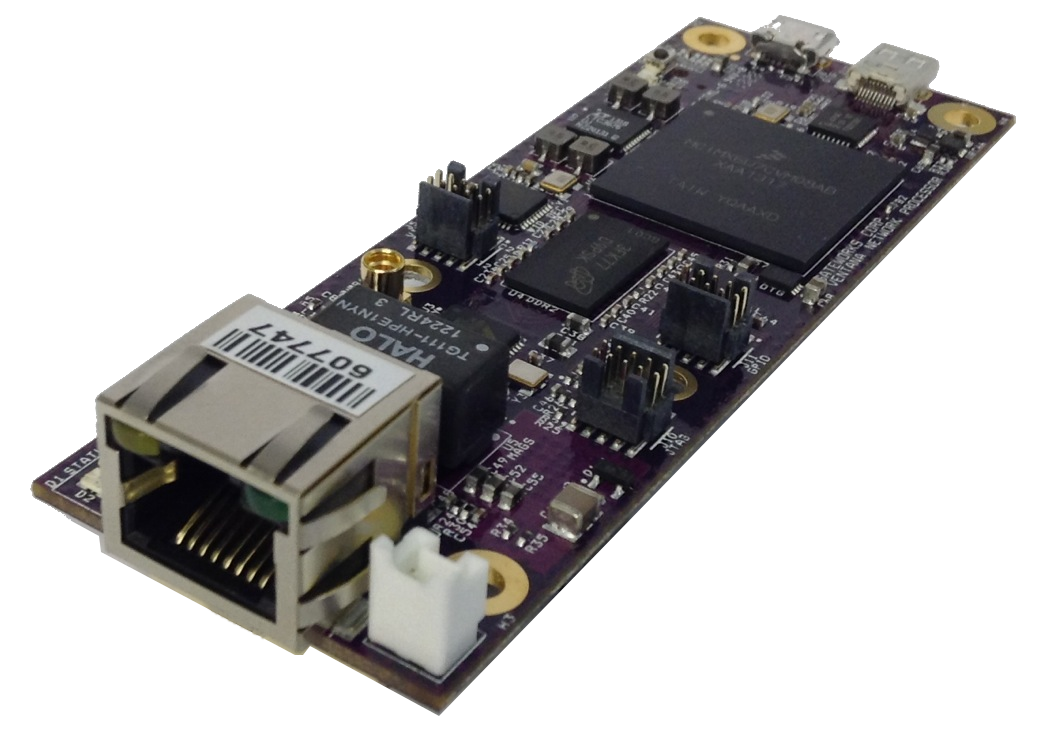

== Choosing a BSP ==

Gateworks offers several Board Support Packages for the Newport Product family. Which one we recommend depends a bit upon what your goal is and what your experience level is

* [#OpenWrtBoardSupportPackageBSP OpenWrt] - '''Coming Soon for Newport''' - intended for wireless routers and access points (low flash and memory footprint)

- '''Recommended for networking users wanting to create a headless router, VPN, basestation, wireless access point and more. Produces by far the smallest storage and memory footprint but users new to Embedded Linux will have a bit of a learning curve'''

- Fairly up-to-date and/or vanilla kernel support

- Latest wireless drivers (via linux-backports)

- Custom application config and init system (nice for small footprint, but can make adding support for additional packages more work)

- Wide variety of packages (including a fairly nice web-admin)

- Console-based build system (expect 60mins to build BSP for a specific board family)

- Downloadable SDK and Toolchain available to build apps on a development host without building the entire BSP

- Pre-built images available

* [#Ubuntu Ubuntu]

- '''Recommended for developers trying to heavily leverage opensource software packages or libraries that are not supported by the other BSP's. This is the most user-friendly for developers new to Embedded Linux but will not produce a very trimmed down filesystem image.'''

- Uses mainline kernel.

- Supports all Newport features.

- Documentation provided to use Ubuntu pre-built packages and debootstrap to create a root filesystem in minutes

- Native compilation: no SDK or cross-toolchain needed

The following table may also help in choosing what BSP is right for you:

||= Feature =||= OpenWrt =||= Ubuntu =||= Notes =||

|| Pre-built images || Yes || Yes || ||

|| Storage Needed || <256MB || 2GB or larger || ||

|| Build-System || Yes || No || 1 ||

|| Toolchain || SDK || Native || 2 ||

|| Web-Admin || Yes || No || 3 ||

1. The OpenWrt BSP contain an integrated build-system. Ubuntu has step-by-step instructions on how to build an bootable system in 10 or so steps.

2. The OpenWrt BSP provides a downloadable SDK for cross-compiling applications on a development hosts. For Ubuntu native development and compilation is supported.

3. The OpenWrt BSP is designed to be a wireless router and has an integrated web-admin for configuration and control.

[=#openwrt]

== OpenWrt Board Support Package (BSP) ==

'''Coming Soon'''

Newport OpenWrt BSP:

* [wiki:newport/openwrt#Step2.InstallingFirmware Pre-Built Binaries]

* [wiki:newport/openwrt Building/Installing OpenWrt w/ Gateworks Patches for the Newport Family]

* [wiki:OpenWrt Main OpenWrt Wiki Page]

* [wiki:OpenWrt/SDK#NewportNotes OpenWrt SDK Toolchain]

* join the [http://www.gateworks.com/mailman/listinfo maillist] to follow activity

* [wiki:OpenWrt/gpio GPIO and LED Configuration]

The Newport OpenWrt BSP provides the following:

* Linux 4.x kernel (fairly vanilla)

* latest wireless drivers (compat-wireless)

* tuned for minimal FLASH/memory footprint (entire distro fits on embedded 16MB FLASH)

[=#ubuntu]

== Ubuntu ==

Gateworks offers a pre-built Ubuntu distribution using the latest Gateworks kernel as well as instructions on how to build your own Ubuntu based distribution.

* [wiki:ventana/ubuntu Ubuntu Wiki and Software]

[=#third_party_linux]

= Third Party Linux Distros =

While Gateworks cannot fully support all Linux distros, it is relatively simple to overlay a Gateworks Newport kernel onto any non-Gateworks third party Linux distro rootfs image.

The following links will describe what is needed:

1. Linux kernel supporting Newport: [wiki:linux/kernel]

2. Root Filesystem: [#rootfs see below]

3. Bootable media: [wiki:linux/blockdev]

[=#rootfs]

=== Root filesystem Sources ===

There are several sources of pre-built root filesystems that are compatible with Newport. As Newport uses an ARM 64bit based SoC, you need to use something that is compatible with an ARMv8 instruction set. Many pre-built distributions will reference 'arm64' which means 'ARM 64-bit' which is appropriate for the CN80XX / CN81XX SoC.

Some popular third-party sources:

* [http://cdimage.ubuntu.com/ubuntu-core/releases/ Ubuntu Core] - this is a minimal filesystem that you can build off of at runtime by adding packages from various repositories.

* [https://releases.linaro.org/ Linaro] - Linaro has several root filesystems including server, nano, developer, core, and ALIP. Each root filesystem will have different things installed for different purposes. Choose carefully which will work for you.

Notes:

* some root filesystems may require you to manually add a user before booting (ie Ubuntu Core)

* the default Newport bootloader expects to find the Image in the /boot directory on the 2nd partition of type ext2/3/4

[=#mainline-linux]

= Mainline Linux Kernel support =

Gateworks actively participates in the development of the Linux kernel.

Cavium licenses CPU core IP from ARM and the name they give the CPU core within the OCTEON-TX CN80XX / CN81XX is the Cavium 'ThunderX'. Therefore many of the peripheral drivers within the Linux kernel have 'thunderx' in their name and more often then not the 'OCTEON' name refers to the older OCTEON MIP64 core.

The following table shows what OCTEON-TX CN80XX / CN81XX peripherals support is available in the mainline kernel starting from 4.13:

||= Feature =||= Support =||= Notes =||

|| [wiki:multicoreprocessing SMP] || Yes || ARCH_THUNDER ||

|| [wiki:serial] UART (SBSA) || Yes || SERIAL_AMBA_PL011 drivers/tty/serial/amba-pl011.c ||

|| [wiki:watchdog] Watchdog (SBSA) || Yes || ARM_SBSA_WATCHDOG drivers/watchdog/sbsa_gwdt.c ||

|| [wiki:I2C I2C] || Yes (4.9+) || I2C_THUNDERX drivers/i2c/busses/i2c-{octeon-core,thunderx-pcidrv}.c ||

|| Networking BGX (SGMII) || Yes (4.2+) || THUNDER_NIC_BGX drivers/net/ethernet/cavium/thunder/thunder_bgx.c ||

|| Networking RGX (RGMII) || Yes (4.9+) || THUNDER_NIC_RGX drivers/net/ethernet/cavium/thunder/thunder_xcv.c ||

|| PCI || Yes (4.6+) || PCI drivers/pci/host/pci-thunder-{ecam,pem}.c ||

|| [wiki:SPI SPI] || Yes (4.9+) || SPI_THUNDERX drivers/spi/spi-thunderx.c ||

|| [wiki:MMC] eMMC / microSD || Yes (4.12+) || MMC_CAVIUM_THUNDERX drivers/mmc/host/thunderx-mmc.c ||

|| HW RNG (Hardware Random Number Generator) || Yes (4.9+) || HW_RANDOM_CAVIUM drivers/char/hw_random/cavium-rng*.c ||

|| HW Compressions offload || Yes (4.12+) || DEV_CAVIUM_ZIP drivers/crypto/cavium/zip.c ||

|| Crypto || Yes (4.11+) || DEV_CAVIUM_CPT drivers/crypto/cavium ||

|| [wiki:gsc#rtc RTC] || Yes || RTC_DRV_DS1672 drivers/rtc/rtc-ds1672.c ||

|| [wiki:gpio LED/GPIO] || Yes (4.14+) || GPIO_THUNDERX drivers/gpio/gpio-thunderx.c ||

|| [wiki:USB USB 3.0] || Yes || USB_XHCI_PCI ||

|| [wiki:sata mSATA] || Yes || SATA_AHCI ||

The following kernel configs should be enabled for the OCTEON-TX CN80XX / CN81XX:

* SERIAL_AMBA_PL011 - ARM SBSA UART

* MMC_CAVIUM_THUNDERX - MMC

* EDAC_THUNDERX - Error Detection and Correction (works with 'edac-util' app from 'edac-utils' package)

* GPIO_THUNDERX - General Purpose I/O

* SPI_THUNDERX - SPI Controller

* I2C_THUNDERX - I2C Controller

* THUNDERX_NIC_VF - NIC virtual function

* THUNDERX_NIC_PF - NIC physical function

* THUNDERX_NIC_BGX - Network Controller (selects MDIO_CAVIUM/MDIO_THUNDERX)

* THUNDERX_NIC_RGX - RGMII Network Controller (selects MDIO_CAVIUM/MDIO_THUNDERX)

* PCI_HOST_THUNDER_PEM - PCI host controller

* PCI_HOST_THUNDER_ECAM - Enhanced Configuration Access Mechanism for PCIe memory mapped I/O

* ARM_SBSA_WATCHDOG - ARMv8 Watchdog

* CRYPTO_DEV_CAVIUM_ZIP - Hardware Compression / Decompression off-load

* HW_RANDOM_CAVIUM - Hardware accelerated random number generator

Note that there are many kernel drivers using the name 'Octeon' but they typically refer to a different chipset and the CN80XX / CN81XX have more in common with the Cavium 'ThunderX' architecture as that is the SoC core.

For details on building a Linux kernel see [wiki:linux/kernel here]

}}}

== Choosing a BSP ==

Gateworks offers several Board Support Packages for the Newport Product family. Which one we recommend depends a bit upon what your goal is and what your experience level is

* [#OpenWrtBoardSupportPackageBSP OpenWrt] - '''Coming Soon for Newport''' - intended for wireless routers and access points (low flash and memory footprint)

- '''Recommended for networking users wanting to create a headless router, VPN, basestation, wireless access point and more. Produces by far the smallest storage and memory footprint but users new to Embedded Linux will have a bit of a learning curve'''

- Fairly up-to-date and/or vanilla kernel support

- Latest wireless drivers (via linux-backports)

- Custom application config and init system (nice for small footprint, but can make adding support for additional packages more work)

- Wide variety of packages (including a fairly nice web-admin)

- Console-based build system (expect 60mins to build BSP for a specific board family)

- Downloadable SDK and Toolchain available to build apps on a development host without building the entire BSP

- Pre-built images available

* [#Ubuntu Ubuntu]

- '''Recommended for developers trying to heavily leverage opensource software packages or libraries that are not supported by the other BSP's. This is the most user-friendly for developers new to Embedded Linux but will not produce a very trimmed down filesystem image.'''

- Uses mainline kernel.

- Supports all Newport features.

- Documentation provided to use Ubuntu pre-built packages and debootstrap to create a root filesystem in minutes

- Native compilation: no SDK or cross-toolchain needed

The following table may also help in choosing what BSP is right for you:

||= Feature =||= OpenWrt =||= Ubuntu =||= Notes =||

|| Pre-built images || Yes || Yes || ||

|| Storage Needed || <256MB || 2GB or larger || ||

|| Build-System || Yes || No || 1 ||

|| Toolchain || SDK || Native || 2 ||

|| Web-Admin || Yes || No || 3 ||

1. The OpenWrt BSP contain an integrated build-system. Ubuntu has step-by-step instructions on how to build an bootable system in 10 or so steps.

2. The OpenWrt BSP provides a downloadable SDK for cross-compiling applications on a development hosts. For Ubuntu native development and compilation is supported.

3. The OpenWrt BSP is designed to be a wireless router and has an integrated web-admin for configuration and control.

[=#openwrt]

== OpenWrt Board Support Package (BSP) ==

'''Coming Soon'''

Newport OpenWrt BSP:

* [wiki:newport/openwrt#Step2.InstallingFirmware Pre-Built Binaries]

* [wiki:newport/openwrt Building/Installing OpenWrt w/ Gateworks Patches for the Newport Family]

* [wiki:OpenWrt Main OpenWrt Wiki Page]

* [wiki:OpenWrt/SDK#NewportNotes OpenWrt SDK Toolchain]

* join the [http://www.gateworks.com/mailman/listinfo maillist] to follow activity

* [wiki:OpenWrt/gpio GPIO and LED Configuration]

The Newport OpenWrt BSP provides the following:

* Linux 4.x kernel (fairly vanilla)

* latest wireless drivers (compat-wireless)

* tuned for minimal FLASH/memory footprint (entire distro fits on embedded 16MB FLASH)

[=#ubuntu]

== Ubuntu ==

Gateworks offers a pre-built Ubuntu distribution using the latest Gateworks kernel as well as instructions on how to build your own Ubuntu based distribution.

* [wiki:ventana/ubuntu Ubuntu Wiki and Software]

[=#third_party_linux]

= Third Party Linux Distros =

While Gateworks cannot fully support all Linux distros, it is relatively simple to overlay a Gateworks Newport kernel onto any non-Gateworks third party Linux distro rootfs image.

The following links will describe what is needed:

1. Linux kernel supporting Newport: [wiki:linux/kernel]

2. Root Filesystem: [#rootfs see below]

3. Bootable media: [wiki:linux/blockdev]

[=#rootfs]

=== Root filesystem Sources ===

There are several sources of pre-built root filesystems that are compatible with Newport. As Newport uses an ARM 64bit based SoC, you need to use something that is compatible with an ARMv8 instruction set. Many pre-built distributions will reference 'arm64' which means 'ARM 64-bit' which is appropriate for the CN80XX / CN81XX SoC.

Some popular third-party sources:

* [http://cdimage.ubuntu.com/ubuntu-core/releases/ Ubuntu Core] - this is a minimal filesystem that you can build off of at runtime by adding packages from various repositories.

* [https://releases.linaro.org/ Linaro] - Linaro has several root filesystems including server, nano, developer, core, and ALIP. Each root filesystem will have different things installed for different purposes. Choose carefully which will work for you.

Notes:

* some root filesystems may require you to manually add a user before booting (ie Ubuntu Core)

* the default Newport bootloader expects to find the Image in the /boot directory on the 2nd partition of type ext2/3/4

[=#mainline-linux]

= Mainline Linux Kernel support =

Gateworks actively participates in the development of the Linux kernel.

Cavium licenses CPU core IP from ARM and the name they give the CPU core within the OCTEON-TX CN80XX / CN81XX is the Cavium 'ThunderX'. Therefore many of the peripheral drivers within the Linux kernel have 'thunderx' in their name and more often then not the 'OCTEON' name refers to the older OCTEON MIP64 core.

The following table shows what OCTEON-TX CN80XX / CN81XX peripherals support is available in the mainline kernel starting from 4.13:

||= Feature =||= Support =||= Notes =||

|| [wiki:multicoreprocessing SMP] || Yes || ARCH_THUNDER ||

|| [wiki:serial] UART (SBSA) || Yes || SERIAL_AMBA_PL011 drivers/tty/serial/amba-pl011.c ||

|| [wiki:watchdog] Watchdog (SBSA) || Yes || ARM_SBSA_WATCHDOG drivers/watchdog/sbsa_gwdt.c ||

|| [wiki:I2C I2C] || Yes (4.9+) || I2C_THUNDERX drivers/i2c/busses/i2c-{octeon-core,thunderx-pcidrv}.c ||

|| Networking BGX (SGMII) || Yes (4.2+) || THUNDER_NIC_BGX drivers/net/ethernet/cavium/thunder/thunder_bgx.c ||

|| Networking RGX (RGMII) || Yes (4.9+) || THUNDER_NIC_RGX drivers/net/ethernet/cavium/thunder/thunder_xcv.c ||

|| PCI || Yes (4.6+) || PCI drivers/pci/host/pci-thunder-{ecam,pem}.c ||

|| [wiki:SPI SPI] || Yes (4.9+) || SPI_THUNDERX drivers/spi/spi-thunderx.c ||

|| [wiki:MMC] eMMC / microSD || Yes (4.12+) || MMC_CAVIUM_THUNDERX drivers/mmc/host/thunderx-mmc.c ||

|| HW RNG (Hardware Random Number Generator) || Yes (4.9+) || HW_RANDOM_CAVIUM drivers/char/hw_random/cavium-rng*.c ||

|| HW Compressions offload || Yes (4.12+) || DEV_CAVIUM_ZIP drivers/crypto/cavium/zip.c ||

|| Crypto || Yes (4.11+) || DEV_CAVIUM_CPT drivers/crypto/cavium ||

|| [wiki:gsc#rtc RTC] || Yes || RTC_DRV_DS1672 drivers/rtc/rtc-ds1672.c ||

|| [wiki:gpio LED/GPIO] || Yes (4.14+) || GPIO_THUNDERX drivers/gpio/gpio-thunderx.c ||

|| [wiki:USB USB 3.0] || Yes || USB_XHCI_PCI ||

|| [wiki:sata mSATA] || Yes || SATA_AHCI ||

The following kernel configs should be enabled for the OCTEON-TX CN80XX / CN81XX:

* SERIAL_AMBA_PL011 - ARM SBSA UART

* MMC_CAVIUM_THUNDERX - MMC

* EDAC_THUNDERX - Error Detection and Correction (works with 'edac-util' app from 'edac-utils' package)

* GPIO_THUNDERX - General Purpose I/O

* SPI_THUNDERX - SPI Controller

* I2C_THUNDERX - I2C Controller

* THUNDERX_NIC_VF - NIC virtual function

* THUNDERX_NIC_PF - NIC physical function

* THUNDERX_NIC_BGX - Network Controller (selects MDIO_CAVIUM/MDIO_THUNDERX)

* THUNDERX_NIC_RGX - RGMII Network Controller (selects MDIO_CAVIUM/MDIO_THUNDERX)

* PCI_HOST_THUNDER_PEM - PCI host controller

* PCI_HOST_THUNDER_ECAM - Enhanced Configuration Access Mechanism for PCIe memory mapped I/O

* ARM_SBSA_WATCHDOG - ARMv8 Watchdog

* CRYPTO_DEV_CAVIUM_ZIP - Hardware Compression / Decompression off-load

* HW_RANDOM_CAVIUM - Hardware accelerated random number generator

Note that there are many kernel drivers using the name 'Octeon' but they typically refer to a different chipset and the CN80XX / CN81XX have more in common with the Cavium 'ThunderX' architecture as that is the SoC core.

For details on building a Linux kernel see [wiki:linux/kernel here]